ΉΦΖΫ≤®’ϊΝς‘ΎΒγ―ΙΒς’ϊΡΘΩι(VRM)÷–ΒΡ”Π”Ο

«ΊΚΘΚη ’≈ΖΫΜΣ ΆθΜέ’ξ ΡœΨ©ΚΫΩ’ΚΫΧλ¥σ―ßΘ®ΡœΨ©210016Θ©

’Σ “ΣΘΚΒγ―ΙΒς’ϊΡΘΩιΘ®VRMΘ© «’κΕ‘ΈΔ¥ΠάμΤςΒ»Βδ–Ά ΐΨί¥ΠάμΒγ¬ΖΩΣΖΔΒΡΒγ‘¥ΡΘΩιΓΘ±ΨΤΣ Ήœ»Ε‘VRMœ÷‘Ύ≥Θ”ΟΒΡΆΊΤΥΫχ––ΝΥΜΊΙΥΘ§÷Η≥ωΝΥΤδ¥φ‘ΎΒΡ»±œίΘ§¥”Εχ“ΐ»κΉΦΖΫ≤®’ϊΝςΒγ¬ΖΘ§≤ΔΕ‘ΤδΙΛΉς‘≠άμΫχ––ΝΥΫι…ήΓΘ”Π”ΟΫΜ¥μ≤ΔΝΣΦΦ θΒΡΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥ‘Ύ δ»κΒγ―ΙΒ»”ΎΝΫ±Ε δ≥ωΒγ―Ι ±ΨΏ”–Ήν”≈ΒΡ–‘ΡήΓΘΒΪΒΆ δ»κΒγ―Ι»¥“ΐ»κΝΥ δ»κ¬Υ≤®ΤςΙΐ¥σΒ»œΒΆ≥…ηΦΤΈ ΧβΓΘΈΣ¥Υ±ΨΈΡΗχ≥ωΝΥΗΏ δ»κΒγ―ΙΓΔΗτάκ ΫQSWΒγ¬ΖΒΡ…ηΦΤΥΦ¬ΖΓΘΖ÷Έω±μΟςΘ§‘ΎΫαΚœ¥≈Φ·≥…ΦΦ θΚσΘ§’β–©Ητάκ ΫQSWΆΊΤΥΨΏ”–Κή”–Έϋ“ΐΝΠΒΡ”Π”ΟΦέ÷ΒΓΘ

ΙΊΦϋ¥ ΘΚ ÷±/÷± ±δΜΜΤς VRM ΉΦΖΫ≤® ΫΜ¥μ≤ΔΝΣ ΒΆ―Ι/¥σΒγΝς

Application of Quasi-Square-Wave Rectification in Voltage Regulator Module(VRM) Topologies

Qin hai hong Zhang fang hua Wang hui zhen

Nanjing University of Aeronautics and Astronautics (210016)

Abstract: The Microprocessors return to low voltage and high current. This imposes difficulties on Voltage Regulator Module(VRM) design. With the review of current VRM topologies, Quasi-Square-Wave (QSW) rectification is presented in detail. Considering the steady state ripple cancellation and transient response, it is ideal for the interleaving QSW VRM to have an input voltage equal to twice the output voltage. However, the low voltage will introduce many problems, especially at the input filter. To solve this problem, high input voltage, fast VRMs with a transformer are proposed. It is expected to have good transient performance and high efficiency, when incorporating integrated magnetics technology.

Key words: dc/dc converter Voltage-Regulator-Module Quasi-Square-Wave interleaving low-voltage/high-current

1 “ΐ ―‘

ΥφΉ≈–≈œΔΦΦ θ≤ζ“ΒΒΡΩλΥΌΖΔ’ΙΘ§ΗΏΥΌ≥§¥σΙφΡΘΦ·≥…Βγ¬Ζ≥Ώ¥γΒΡ≤ΜΕœΦθ–ΓΘ§ΦΤΥψΜζΓΔΙΛΉς’ΨΓΔΆχ¬γΖΰΈώΤςΓΔ±ψ–· Ϋ…η±ΗΒΟΒΫ―ΗΟΆΒΡΖΔ’ΙΓΘ‘Ύ’β–©≥ΓΚœΘ§ΙψΖΚΒΡ≤…”Ο÷±ΝςΖ÷≤Φ ΫΒγ‘¥œΒΆ≥ΓΘΙΙ≥…’β–©Βγ‘¥œΒΆ≥ΒΡΙΊΦϋ≤ΩΦΰ «Ης÷÷≤ΜΆ§ΦΦ θΙφΗώΒΡDC/DC±δΜΜΤςΡΘΩιΓΘΕχ’β–©ΦΤΥψΜζΓΔΆ®―Ε≤ζΤΖΒΡΚΥ–Ρ≤ΩΦΰ «ΈΔ¥ΠάμΤςΒ»Βδ–ΆΒΡ ΐΨί¥ΠάμΒγ¬ΖΓΘΕ‘”ΎΤδΙ©ΒγΒγ‘¥ά¥ΥΒΘ§’β–© ΐΨί¥ΠάμΒγ¬ΖΙΙ≥…“ΜάύΧΊ βΒΡΗΚ‘ΊΘ§ΙΛΉςΒγ―ΙΫœΒΆΓΔΒγΝςΫœ¥σΘ§Ης÷÷ΙΛΉςΉ¥Χ§œύΜΞΉΣΜΜ ±Ε‘”ΠΒΡΒγΝς±δΜ·¬ ΚήΗΏΓΘ“‘Βδ–ΆΒΡInterl PentiumΈΔ¥ΠάμΤςΈΣάΐΘ§ΡΩ«ΑΤδΙΛΉς÷ςΤΒ‘Ύ1GHz“‘…œΘ§Ι©ΒγΒγ―Ι‘Ύ2VΓΣ3.5V÷°ΦδΘ§’β“ΜΙΛΉςΒγ―Ι”…ΦΤΥψΜζΓΑ“χΚ–Γ±÷–ΒΡ5VΜρ12VΒγ―ΙΘ§Ψ≠ΙΐΫœ≥ΛΒΡ¥Ϊ δœΏ“ΐ≥ωΘ§Ά®Ιΐ¥ΠάμΤςΗΫΫϋΒΡBUCK±δΜΜΤςΫχ––Βγ―Ι±δΜΜΚσΒΟΒΫΓΘ

ΈΣΝΥΫχ“Μ≤ΫΧαΗΏΈΔ¥ΠάμΤςΒ» ΐΨί¥ΠάμΒγ¬ΖΒΡΥΌΕ»Θ§ Βœ÷ΗϋΦ”ΩλΥΌ”––ßΒΡ ΐΨί¥ΠάμΘ§ΤδΙΛΉςΤΒ¬ ΫΪΫχ“Μ≤ΫΧαΗΏΘ§Ι©ΒγΒγ―ΙΫΪ‘Ϋά¥‘ΫΒΆΘ§Εχ«“ΥφΉ≈Φ·≥…Ε»ΒΡ≤ΜΕœΧαΗΏΘ§‘Ϋά¥‘ΫΕύΒΡ¥ΠάμΤςΦ·≥…Βγ¬ΖΫΪΦ·≥…‘ΎΆ§“ΜΗω–ΨΤ§…œΘ§“ρ¥Υœ¬“Μ¥ζΈΔ¥ΠάμΤςΒΡΕνΕ®ΙΛΉςΒγΝςΫΪ¥οΒΫ50A~100AΘ§…θ÷ΝΗϋΗΏΘ§“Σ«σΈΔ¥ΠάμΤς”–―œΗώΒΡΙΠ¬ Ιήάμ¥κ ©ΓΘΥυ”–’β–©Ε‘ΈΔ¥ΠάμΤς’βάύΒδ–ΆΗΚ‘ΊΒΡΙ©ΒγΒγ‘¥Χα≥ωΝΥΗϋΗΏΒΡ“Σ«σΓΘΡΩ«ΑΙζΆβΚήΕύ―–ΖΔΜζΙΙΓΔΙΪΥΨ“―Ψ≠’κΕ‘ΗΏΥΌΈΔ¥ΠάμΤς’βάύΧΊ βΗΚ‘ΊΒΡΙ©ΒγΒγ‘¥Ϋχ––ΝΥΙψΖΚ…ν»κΒΡ―–ΨΩΘ§≤ΔΑ―’β“Μ―–ΨΩ»»ΒψΘ§Ηχ“‘Ή®Ο≈ΒΡΟϊ≥ΤVRMΘ§Φ¥Βγ―ΙΒς’ϊΡΘΩιΓΘ’κΕ‘ΈΔ¥ΠάμΤςΒ»ΗΏΥΌ ΐΨί¥ΠάμΒγ¬ΖΒΡΧΊΒψΘ§“Σ«σVRMΧαΙ©Ψ≠Ιΐ―œΗώΒς’ϊΒΡΒΆ―ΙΚΆ¥σΒγΝς δ≥ωΘ§ΨΏ”–ΩλΥΌΒΡΕ·Χ§œλ”ΠΓΘ

2 VRMœ÷”ΟΆΊΤΥΒΡΜΊΙΥΘΚ

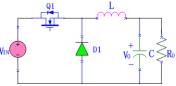

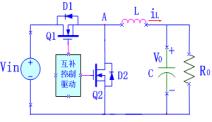

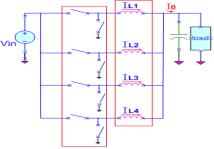

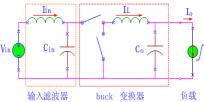

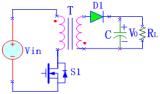

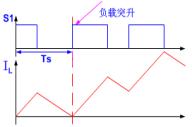

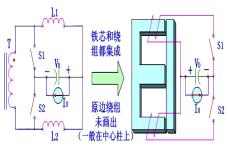

œ÷ΫώVRM¥σΕύ≤…”Ο≥ΘΙφBuckΜρΆ§≤Ϋ’ϊΝςBuckΆΊΤΥΓΘ»γΆΦ1Υυ ΨΘ§(a)ΈΣ≥ΘΙφBuckΆΊΤΥΘ§”ΟSchottkyΉςΈΣ’ϊΝςΙήΘ§(b)ΈΣΆ§≤Ϋ’ϊΝςBuckΆΊΤΥΘ§”ΟΒΆΒΦΆ®ΒγΉηΒΡΒΆ―ΙΙΠ¬ MOSFETΘ§¥ζΧφschottkyΉςΈΣΆ§≤Ϋ’ϊΝςΙήΘ§Τδ÷–Θ§Ά§≤Ϋ’ϊΝςΙήQ2”κ÷ςΙήQ1ΒΡΩΣΙΊ–≈Κ≈ΜΞ≤ΙΓΘ

ΆΦ1 (a) ≥ΘΙφBuckΆΊΤΥ Θ®bΘ© Ά§≤Ϋ’ϊΝςBuck

ΈΣ”≈Μ·ΩΊ÷ΤΜΖ≤Έ ΐ…ηΦΤΘ§œΘΆϊ‘Ύ’ϊΗωΗΚ‘Ί±δΜ·ΖΕΈßΡΎΘ§÷ςΒγ¬ΖΡήΙΜ‘ΎΒΞΡΘ Ϋœ¬ΙΛΉςΓΘΕ‘”ΎBuck–ΆΆΊΤΥΘ§ΙΛΉς”ΎΝ§–χΡΘ Ϋ(CCM)Ά®≥ΘΩ…“‘ΜώΒΟΉνΚΟΒΡ–‘ΡήΘ§Υυ“‘‘Ύ…ηΦΤBuck–Ά±δΜΜΤς ±Θ§“ΜΑψΑ¥’’CCMΙΛΉςΡΘ Ϋ…ηΦΤΓΔ―Γ‘ώΒγ¬Ζ≤Έ ΐΓΘ‘Ύ―Γ‘ώ δ≥ω¬Υ≤®ΒγΗ– ±Θ§“ΜΑψ»Γ“ΜΗωΉν–ΓΗΚ‘ΊΒγΝςI0minΘ§±Θ÷Λ‘Ύ¥σ”ΎI0minΒΡΥυ”–ΗΚ‘ΊΖΕΈßΡΎΘ§ΒγΗ–ΒγΝςΕΦΡήΝ§–χΘ®≤ΜΒΫ¥οΝψΈΜΘ©ΓΘΆ®≥ΘΗυΨί“‘œ¬ΙΪ ΫΫχ––ΦΤΥψΘΚ

Θ®’βάοΘ§I0min»ΓΈΣ¬ζ‘ΊΒγΝςΒΡ10%Θ©

Θ®’βάοΘ§I0min»ΓΈΣ¬ζ‘ΊΒγΝςΒΡ10%Θ©

ΒΟΒΫΘΚ  (1)

(1)

Τδ÷–Θ§DΈΣ’ΦΩ’±»Θ§VinΈΣ δ»κΒγ―ΙΘ§VoΈΣ δ≥ωΒγ―ΙΓΘIoΈΣ¬ζ‘ΊΒγΝςΘ§fsΈΣΩΣΙΊΤΒ¬ ΓΘ

ΙΪ Ϋ(1)ΦΤΥψΥυΒΟΒΡΒγΗ–÷ΒΫœ¥σ(Βδ–Ά÷ΒΈΣ2µH~4µH)Θ§œό÷ΤΝΥΙΠ¬ ΦΕΡήΝΩ¥Ϊ δΥΌΕ»ΓΘ»τΈΣΧαΗΏΡήΝΩ¥Ϊ δΥΌΕ»Θ§«Ω––Φθ–ΓΒγΗ–ΝΩΘ§‘ρΜα ΙΒγ¬Ζ‘ΎΗϋ¥σΒΡΗΚ‘ΊΖΕΈßΡΎΘ®I0min‘ω¥σΘ©ΙΛΉς”ΎDCMΉ¥Χ§Θ§ΕχΑ¥’’CCMΙΛΉςΡΘ Ϋ―Γ»ΓΒΡΩΊ÷ΤΒγ¬Ζ≤Έ ΐΘ§Ρ―“‘Ά§ ±¬ζΉψDCMΡΘ ΫΒΡ“Σ«σΘ§÷¬ ΙDCMΙΛΉςΉ¥Χ§œ¬Βγ¬Ζ–‘Ρή±δ≤νΘ§…θ÷Ν“ΐΤπ≤ΜΈ»Ε®ΘΜ»τΦφΙΥCCMΚΆDCMΝΫ÷÷ΙΛΉςΉ¥Χ§Θ§’έ÷‘―Γ»ΓΩΊ÷Τ≤Έ ΐΘ§‘ρ”÷Μα“‘Έΰ…ϋCCMΉ¥Χ§œ¬ΒΡΒγ¬Ζ–‘ΡήΈΣ¥ζΦέΓΘΩ…ΦϊΘ§Α¥¥ΪΆ≥…ηΦΤΖΫΖ®ΙΛΉςΒΡBuck±δΜΜΤςΆΊΤΥΘ§“ρ¥σ δ≥ω¬Υ≤®ΒγΗ–ΒΡ¥φ‘ΎΘ§œό÷ΤΝΥΙΠ¬ ΦΕΡήΝΩ¥Ϊ δΥΌΕ»Θ§ΗΚ‘ΊΥ≤Χ§±δΜ·Υυ–η“ΣΘ®Μρ≤ζ…ζΘ©ΒΡΡήΝΩΦΗΚθ»Ϊ≤Ω”…¬Υ≤®Βγ»ίΧαΙ©Θ®ΜρΈϋ ’Θ©ΓΘΈΣ Ι δ≥ωΒγ―Ι≤Μ÷¬≥§≥ωΥυ‘ –μΒΡ±δΜ·ΖΕΈßΘ§ΨΆ±Ί–κ‘ωΦ” δ≥ω¬Υ≤®Βγ»ίΘ®“ΜΑψ≤…”ΟΕύΒγ»ί≤ΔΝΣ“‘Φθ–ΓESRΚΆESLΘ©Θ§ ΙΒγ‘¥ΒΡΧεΜΐ÷ΊΝΩ‘ω¥σΘ§ΙΠ¬ ΟήΕ»ΫΒΒΆΘ§“≤‘ωΦ”ΝΥ’ϊΜζ÷Τ‘λ≥…±ΨΓΘ”…¥ΥΩ…ΦϊΘ§Ά§≤Ϋ’ϊΝςBuckΒγ¬ΖΡ―“‘¬ζΉψ–¬“Μ¥ζΈΔ¥Πάμ–ΨΤ§ΖΔ’ΙΕ‘Βγ‘¥ΒΡ“Σ«σΓΘ

ΨΓΙήΧαΗΏΩΣΙΊΤΒ¬ Ω…“‘Φθ–Γ¬Υ≤®ΒγΗ–Θ§ΧαΗΏVRMΒΡΕ·Χ§œλ”ΠΥΌΕ»Θ§ΒΪΆ§ ±“≤¥χά¥ΝΥΗϋΕύΡ―“‘ΫβΨωΒΡΈ ΧβΓΘ»γΘΚ±δΜΜΤςΒΡΩΣΙΊΥπΚΡΚΆ«ΐΕ·ΥπΚΡΥφΉ≈ΤΒ¬ ΒΡ…ΐΗΏ¥σ¥σ‘ωΦ”Θ§¥≈–‘‘ΣΦΰΚΆΙΠ¬ ΤςΦΰΒΡ–‘Ρή±δ≤νΒ»ΓΘ”–ΙΊΈΡœΉ[3]±μΟςΘΚ≤…”ΟΆ§≤Ϋ’ϊΝςBuck±δΜΜΤςΘ§±Ί–κΑ―ΩΣΙΊΤΒ¬ ΧαΗΏΒΫ °ΦΗMHzΒΡΝΩΦΕΘ§≤≈Ρή¬ζΉψœ¬“Μ¥ζΈΔ¥ΠάμΤςΒΡΙΛΉς“Σ«σΘ§Εχ‘Ύ»γ¥ΥΗΏΒΡΩΣΙΊΤΒ¬ œ¬Θ§Μυ”Ύœ÷”–ΦΦ θΒΡΙΠ¬ ΤςΦΰΚΆ¥≈–‘‘ΣΦΰΫΪ≤Μ‘Ό ”ΟΘ§Φ¥±ψΡήΙΜ Ι”ΟΘ§ΙΠ¬ ΤςΦΰΒΡΥπΚΡ“≤ΜαΖ«≥ΘΗΏΘ§ ΙΒΟ’ϊΜζ–߬ ‘Ε‘ΕΒΆ”Ύ÷Η±ξ“Σ«σΘ§≤ΜΡή¬ζΉψ”Π”Ο≥ΓΚœΒΡ–η“ΣΓΘ

ΈΣΝΥΩΥΖΰΆ§≤Ϋ’ϊΝςBuckΒγ¬Ζ‘ΎΥ≤Χ§œλ”ΠΒ»ΖΫΟφ¥φ‘ΎΒΡ≤ΜΉψΘ§”Π‘ΥΕχ…ζΉΦΖΫ≤®’ϊΝςΙΛΉςΖΫ ΫΒΡΆΊΤΥΓΘœ¬ΟφΕ‘ΉΦΖΫ≤®’ϊΝςΒΡΙΛΉς‘≠άμΦΑΤδΧΊΒψΫχ––Ϋι…ήΓΘ

3 ΉΦΖΫ≤®’ϊΝςΘΚ

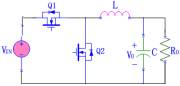

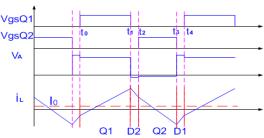

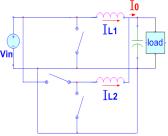

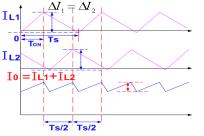

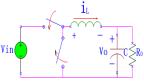

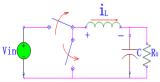

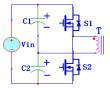

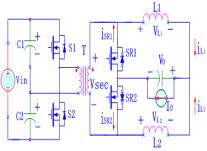

ΆΦ2Ηχ≥ωΝΥΉΦΖΫ≤®’ϊΝςBuckΒγ¬ΖΘ§ΤδΒγ¬ΖΫαΙΙ”κΆ§≤Ϋ’ϊΝςBuckΒγ¬ΖœύΆ§ΓΘΆΦ3Ηχ≥ωΤδΙΛΉς‘≠άμ≤®–ΈΘ§‘ΎΖ÷ΈωΙΛΉς‘≠άμ÷°«ΑΘ§ΙφΕ®MOSFETΧεΕΰΦΪΙήΒΦΆ®―ΙΫΒΈΣVDΘ§MOSFETΙΒΒάΒΦΆ®―ΙΫΒΈΣVfΓΘ“ΜΗωΩΣΙΊ÷ήΤΎΖ÷ΈΣΥΡΗωΩΣΙΊΡΘΧ§Χ÷¬έΓΘ

ΆΦ2 ΉΦΖΫ≤®’ϊΝςBuckΒγ¬Ζ ΆΦ3 QSW’ϊΝςΙΛΉς‘≠άμ≤®–Έ

ΡΘΧ§1Θ®t0---t1Θ©ΘΚ

t0 ±ΩΧΘ§Q1ΒΦΆ®Θ§ΒγΗ–¥ΔΡήΘ§ΒγΗ–ΒγΝς¥”ΗΚΒΫ’ΐ÷πΫΞ…œ…ΐΓΘ

(2)

(2)

t1 ±ΩΧΘ§Q1ΙΊΕœΘ§ΒγΗ–ΒγΝςΒΫ¥οΉν¥σ÷ΒΘ§ΡΘΧ§1Ϋα χΓΘ

ΡΘΧ§2Θ®t1---t2Θ©ΘΚ

¥” Q1ΙΊΕœΘ§÷±÷Ν Q2ΩΣΆ®÷°«ΑΘ§ΒγΗ–ΒγΝςΝςΙΐQ2ΒΡΧεΕΰΦΪΙήD2–χΝςΘ§ΒγΗ–ΒγΝςœ¬ΫΒΓΘ

(3)

(3)

ΡΘΧ§3Θ®t2---t3Θ©ΘΚ

t2 ±ΩΧΘ§Q2ΒΦΆ®Θ®ΝψΒγ―ΙΩΣΆ®Θ©Θ§ΒγΗ– ΆΖ≈ΡήΝΩΘ§ΒγΗ–ΒγΝς¥”’ΐΒΫΗΚ÷πΫΞΫΒΒΆΓΘ

(4)

(4)

t3 ±ΩΧΘ§Q2ΙΊΕœΘ§ΒγΗ–ΒγΝςΒΫ¥οΉνΒΆΒψΓΘ

ΡΘΧ§4Θ®t3---t4Θ©ΘΚ

¥”Q2ΙΊΕœΘ§÷±÷ΝQ1ΩΣΆ®÷°«ΑΘ§ΒγΗ–ΒγΝςΝςΙΐQ1ΒΡΧεΕΰΦΪΙήD1Θ§‘λΨΆQ1ΝψΒγ―ΙΩΣΆ®ΒΡΧθΦΰΓΘ

(5)

(5)

t4 ±ΩΧΘ§Q1‘Ό¥ΈΩΣΆ®Θ®ΝψΒγ―ΙΩΣΆ®Θ©Θ§“ΜΗωΆξ’ϊ÷ήΤΎΫα χΓΘ

ΉΦΖΫ≤®’ϊΝςΖΫ Ϋ±Θ÷Λ‘ΎΥυ”–ΗΚ‘Ί±δΜ·ΖΕΈßΡΎΘ§ΒγΗ–ΒγΝςΕΦΝ§–χΘ®¥”’ΐΒΫΗΚ±δΜ·Θ©Θ§ δ≥ω¬Υ≤®ΒγΗ–ΒΡΗ–÷ΒΑ¥ΤδΒγΝςΖεΖε÷Β «ΝΫ±ΕΒΡ¬ζ‘ΊΒγΝςά¥―Γ»ΓΘΚ

(6)

(6)

±»ΫœΙΪ Ϋ(1)ΚΆ(6) ΫΩ…ΦϊΘ§”κΆ§≤Ϋ’ϊΝςBuckœύ±»Θ§ΉΦΖΫ≤®’ϊΝςΆΊΤΥΒΡ δ≥ω¬Υ≤®ΒγΗ–ΫΒΒΆΝΥ10±ΕΉσ”“Θ§¥σ¥σΧαΗΏΝΥΙΠ¬ ΦΕΒΡœλ”ΠΥΌΕ»ΓΘΕχ«“¥”‘≠άμΖ÷Έω“≤Ω…Ω¥ΒΫΘ§Q1ΚΆQ2ΨυΩ… Βœ÷ΝψΒγ―ΙΩΣΆ®Θ§¥σ¥σΦθ–ΓMOSFETΟήά’–ß”ΠΒΡ”ΑœλΘ§ΫΒΒΆΝΥΩΣΙΊΥπΚΡΚΆ’ΛΦΪ«ΐΕ·ΥπΚΡΓΘ

ΒΪQSWΒγ¬Ζ“≤¥φ‘ΎΫœΕύΈ ΧβΘ§÷ς“Σ±μœ÷‘ΎΘΚ ΔΌ δ≥ω¬Υ≤®ΒγΗ–ΒγΝςΈΤ≤®Ϋœ¥σΘ§ ΙΝςΙΐΩΣΙΊΙήΒΡΒγΝς”––ß÷Β‘ω¥σΘ§Ά®Χ§ΥπΚΡ‘ωΦ”ΘΜ ΔΎ –η“ΣΚή¥σΒΡ δ≥ω¬Υ≤®Βγ»ί¬Υ≥ΐΈΤ≤®ΘΜ Δέ ¥σΒΡΈΤ≤®ΒγΝς“ύ Ι¥≈–‘‘ΣΦΰΒΡΥπΚΡ‘ωΦ”Θ§ Ι”Π”ΟQSWΆΊΤΥΒΡVRM’ϊΜζ–߬ ΒΆ”ΎΆ§≤Ϋ’ϊΝςBuckΆΊΤΥΓΘ

ΈΣΝΥΦθ–ΓQSWΒγ¬Ζ δ≥ωΒγΝςΒΡΈΤ≤®Θ§Ά§ ±”÷Ρή¬ζΉψΩλΥΌΥ≤Χ§œλ”ΠΒΡ“Σ«σΘ§ΫαΚœΫΜ¥μ≤ΔΝΣΦΦ θΘ§”÷”Π‘ΥΕχ…ζΓΑΕύΆ®ΒάΫΜ¥μ≤ΔΝΣΉΦΖΫ≤®’ϊΝςΓ±ΆΊΤΥΓΘ

4 ΕύΆ®ΒάΫΜ¥μ≤ΔΝΣΉΦΖΫ≤®’ϊΝςΘΚ

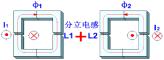

ΥυΈΫΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΘ§Φ¥”Π”ΟΫΜ¥μ≤ΔΝΣΦΦ θΘ§≤…”ΟΕύΗωQSWΆΊΤΥΘ®ΟΩ“ΜΗωQSWΆΊΤΥ≥Τ÷°ΈΣΓΑΒΞΆ®ΒάΓ±Θ©Θ§»Ο≤ΜΆ§Ά®Βά÷–ΩΣΙΊΙήΒΡΩΣΙΊ ±–ρœύΜΞ¥μΩΣ“ΜΕ®ΒΡΫ«Ε»Θ§Α―’β–©Ά®Βά≤ΔΝΣΤπά¥ΙΛΉςΓΘ’βΨΆ ΙΒΟ‘ΎΕύΗωΆ®Βά≤ΔΝΣ ±Θ§ΗςΆ®ΒάΒΡΒγΗ–ΒγΝςΡήΙΜœύΜΞ¥μΩΣ“ΜΕ®ΒΡΫ«Ε»Θ§ Βœ÷ΒγΝςΈΤ≤®ΜΞœϊΉς”ΟΘ§¥”Εχ¥οΒΫΦθ–Γ δ≥ωΒγΝςΈΤ≤®ΒΡΡΩΒΡΓΘœ¬Οφ“‘ΥΪΆ®Βά≤ΔΝΣΚΆΥΡΆ®Βά≤ΔΝΣΒΡ«ιΩωΈΣάΐΫχ––ΝΥΥΒΟςΓΘ

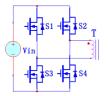

4.1 ΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣΘΚ

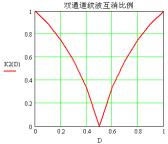

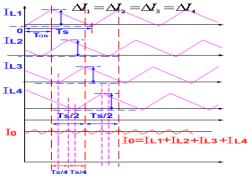

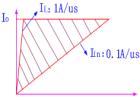

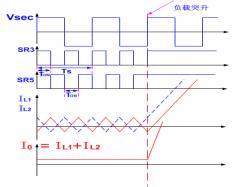

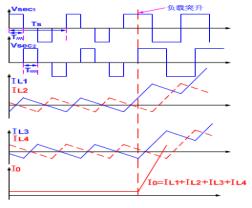

»γΆΦ4Υυ ΨΘ§ΈΣΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥΘ§ΦΑΤδΒγΗ–ΒγΝςΫΜ¥μΒΰΦ” Ψ“βΆΦΓΘΥΪΆ®Βά÷–ΒΡΒγΗ–ΒγΝςœύ≤ν180oœύΈΜΘ§ΈΤ≤®ΜΞœϊ±»άΐK (I0ΈΤ≤®ΖεΖε÷Β”κIL1Μρ IL2ΈΤ≤®ΖεΖε÷ΒΒΡ±»÷Β)ΈΣΘΚ

(7)

(7)

Ε‘”ΠΒΡΙΊœΒ»γΆΦ5(a)Υυ ΨΓΘ¥”ΆΦ5(a)Ω…“‘÷±ΙέΒΡΩ¥≥ωΘ§‘ΎΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥ÷–Θ§÷Μ”–Β±’ΦΩ’±»D=0.5Θ§Φ¥Vin=2V0 ±Θ§≤≈”–Άξ»ΪΒΡΈΤ≤®ΜΞœϊΉς”ΟΘ® δ≥ωΒγΝς Βœ÷ΝψΈΤ≤®Θ©ΓΘ

ΆΦ4 (a) ΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣQSW (b) ΒγΗ–ΒγΝςΫΜ¥μΒΰΦ” Ψ“βΆΦ

4.2 ΥΡΆ®ΒάΫΜ¥μ≤ΔΝΣΘΚ

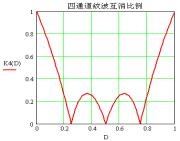

»γΆΦ6Υυ ΨΘ§ΈΣΥΡΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥΘ§ΦΑΤδΒγΗ–ΒγΝςΫΜ¥μΒΰΦ” Ψ“βΆΦΓΘΥΡΆ®Βά÷–ΒΡΒγΗ–ΒγΝςΝΫΝΫœύ≤ν90oœύΈΜΘ§ΈΤ≤®ΜΞœϊ±»άΐKΈΣΘΚ

(8)

(8)

ΆΦ5 (a) ΥΪΆ®ΒάΈΤ≤®ΜΞœϊ±»άΐ (b) ΥΡΆ®ΒάΈΤ≤®ΜΞœϊ±»άΐ

Ε‘”ΠΒΡΙΊœΒ»γΆΦ5(b)Υυ ΨΓΘ¥”ΆΦ5(b)Ω…“‘÷±ΙέΒΡΩ¥≥ωΘ§‘ΎΥΡΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥ÷–Θ§÷Μ”–Β±’ΦΩ’±»ΈΣ0.25ΓΔ0.5ΓΔ0.75 ±Θ§ΈΤ≤®≤≈Ω…“‘Άξ»ΪΜΞœϊΓΘ»γΙϊ’ΦΩ’±»≤ΜΒ»”Ύ“‘…œ÷ΒΘ§÷ΜΡή Βœ÷≤ΩΖ÷ΈΤ≤®ΜΞœϊΓΘ

ΆΦ6 (a)ΥΡΆ®ΒάΫΜ¥μ≤ΔΝΣQSW (b)ΒγΗ–ΒγΝςΫΜ¥μΒΰΦ” Ψ“βΆΦ

4.3 ΫΜ¥μ≤ΔΝΣQSWΒγ¬ΖΒΡΧΊΒψΖ÷ΈωΘΚ

(1)”≈Μ·ΒΡ δ»κ”κ δ≥ωΒγ―ΙΙΊœΒΘΚVin=2V0

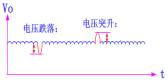

”…«ΑΖ÷ΈωΩ…÷Σ‘ΎΥΪΓΔΥΡΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΒγ¬Ζ÷–Θ§Β±D=0.5 ±Θ§ΕΦΩ…“‘ΜώΒΟΕύΆ®ΒάΒγΗ–ΒγΝςΈΤ≤®ΒΡΆξ»ΪΜΞœϊΉς”ΟΓΘ»γΙϊΑ―D=0.5Θ®Ε‘”Π¥Υ ±ΒΡVin”κV0ΒΡΙΊœΒΈΣVin=2V0Θ©ΉςΈΣΈ»Χ§’ΦΩ’±»Θ§ΫΪΜα Βœ÷Έ»Χ§ΙΛΉς ±ΒΡ δ≥ωΒγΝςΝψΈΤ≤®Θ§¥σ¥σΦθ«α δ≥ω¬Υ≤®Βγ»ίΒΡΈ»Χ§ΈΤ≤®…ηΦΤ―ΙΝΠΓΘΕχ«“Β±Vin=2V0 ±Θ§Βγ¬ΖΩ…“‘ Βœ÷Ε‘≥ΤΒΡΥ≤Χ§œλ”ΠΘ®»γΆΦ7Υυ ΨΘ©ΘΚ

ΔΌ ΗΚ‘ΊΆΜΦ”ΘΚ≥ωœ÷ δ≥ωΒγ―Ιœ¬≥εΘ§ΈΣΦΑ ±œλ”ΠΩ… Βœ÷D=1¬ζ’ΦΩ’±»ΙΛΉςΘ§’ϊΗωΩΣΙΊ÷ήΤΎ δ≥ω¬Υ≤®ΒγΗ–…œΒΡ―ΙΫΒΕΦΈΣ  Θ§ ΙΒγΗ–ΒγΝς―ΗΥΌΧα…ΐΘ§Ε‘”Π

Θ§ ΙΒγΗ–ΒγΝς―ΗΥΌΧα…ΐΘ§Ε‘”Π  ΘΜ

ΘΜ

ΔΎ ΗΚ‘ΊΆΜ–ΕΘΚ≥ωœ÷ δ≥ωΒγ―Ι…œ≥εΘ§ΈΣΦΑ ±œλ”ΠΘ§’ΦΩ’±»Ω…“‘ΫΒΈΣD=0ΙΛΉςΘ§Ε‘”Π’ϊΗωΩΣΙΊ÷ήΤΎΘ§ δ≥ω¬Υ≤®ΒγΗ–…œΒΡ―ΙΫΒΕΦΈΣΘ≠V0Θ§ ΙΒγΝς―ΗΥΌœ¬ΫΒΘ§Ε‘”Π  ΓΘ

ΓΘ

“ρ¥Υ¥”ΫΜ¥μ≤ΔΝΣQSWΆΊΤΥ±Ψ…μά¥Ω¥Θ§‘Ύ¬ζΉψVin=2V0ΒΡ«ιΩωœ¬Θ§VRM δ≥ωΒγ―ΙΒΡ…œ≥εΚΆœ¬≥εΨΏ”–Ε‘≥ΤΒΡΖυ÷ΒΘ§¬Υ≤®≤Έ ΐΩ…“‘ Βœ÷”≈Μ·…ηΦΤΓΘVin=2V0ΫœΨΏΈϋ“ΐΝΠΓΘ

ΆΦ7 (a) ΗΚ‘ΊΆΜΦ” (b) ΗΚ‘ΊΆΜ–Ε (c) δ≥ωΒγ―ΙΙΐ≥ε

(2) Vin=2V0‘Ύ’ϊΗωΒγ‘¥œΒΆ≥÷–ΒΡ»±œίΘΚ

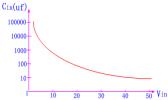

»γΆΦ8Θ§ΈΣVRMΥυ”ΟΒΞΆ®ΒάQSWΒγ¬ΖΒΡΒδ–ΆΫαΙΙ Ψ“βΆΦΓΘΈΣΝΥΦθ–ΓΗΚ‘ΊΆΜ±δΕ‘ΦΤΥψΜζΒγ‘¥œΒΆ≥÷–ΤδΥϋ≤ΩΦΰ(”κVRMΙΪ”ΟΉήœΏ≤ΩΦΰ) δ»κΒγ―ΙΒΡ”ΑœλΘ§±Ί–κ‘ΎVRM δ»κΕΥΦ”“ΜΗωΫœ¥σΒΡ δ»κ¬Υ≤®ΤςΘ§¥Δ¥φΉψΙΜΕύΒΡΡήΝΩΘ§“‘±Θ÷Λ‘ΎΗΚ‘ΊΆΜ±δΤΎΦδΙΪ”ΟΉήœΏΒγ―Ι≤Μ ή”ΑœλΓΘΘ®“ΜΑψΒΡΘ§ΈΣ ΙΗΚ‘Ί÷°ΦδΒΡœύΜΞ”ΑœλΉν–ΓΘ§“Σ«σVRM δ»κΒγΝς±δΜ·¬ ±Ί–κ–Γ”Ύ0.1A/usΘ§’βΗω“Σ«σ“≤ΨΆ≥…ΈΣVRM δ»κ¬Υ≤®Τς…ηΦΤΒΡ“άΨίΓΘΘ©

‘ΎΗΚ‘ΊΆΜ…ΐ ±Θ§ δ≥ω¬Υ≤®Τς–η“ΣœρΗΚ‘ΊΧαΙ©ΡήΝΩΘ§Ά§ ± δ»κ¬Υ≤®Τς‘Ύ±Θ÷Λ δ»κΒγΝς–±¬ –Γ”Ύ0.1A/usΒΡ«ιΩωœ¬Θ§±Ί–κœρ δ≥ω¬Υ≤®ΤςΧαΙ©ΡήΝΩΓΘ–η“Σ”… δ»κ¬Υ≤®Βγ»ίΧαΙ©ΒΡΡήΝΩ»γΆΦ9Υυ ΨΘ§Ε‘”ΠΙΊœΒΈΣ

(9)

(9)

Τδ÷–Θ§SR(Iin) « δ»κΒγΝς±δΜ·¬ Θ§ΠΛVin « δ»κΒγ―Ι±δΜ·ΖΕΈßΘ§Vin « δ»κΒγ―ΙΘ§P0 « δ≥ωΙΠ¬ ΓΘ

δ»κΒγ»ίCin”κ δ»κΒγ―ΙVinΒΡΕ‘”ΠΙΊœΒ«ζœΏ»γΆΦ9Υυ ΨΓΘΥφΉ≈¥ΠάμΤςΙΛΉςΒγ―ΙΒΡΫχ“Μ≤ΫΫΒΒΆΘ®Ήν–¬“―Χα≥ω1V“‘œ¬ΒΡ“Σ«σΘ©Θ§»γΙϊΑ¥’’Vin=2V0ΒΡ”≈Μ·ΙΊœΒΘ§VRMΒΡ δ»κΒγ―ΙΫωΈΣ2VΉσ”“Θ§ΫΪ–η“ΣΚή¥σΒΡ δ»κ¬Υ≤®Βγ»ίΘ§¥οΒΫmFΝΩΦΕΘΜΕχΒ± δ»κΒγ―Ι…ΐΗΏ ±Θ§’β“ΜCinΫΪ”κVin≥…ΤΫΖΫΖ¥±»ΒΡΙΊœΒΥΌΦθΓΘΕ‘”ΠVinΧαΗΏΈΣ48VΉσ”“ ±Θ§CinΒΡΝΩΦΕ“―Ψ≠ΫΒΈΣΦΗ °ΗωΠΧFΘ§¥”Εχ ΙΒΟVRMΒΡ’ϊΜζ≥Ώ¥γΡήΙΜ¬ζΉψ‘Ϋά¥‘Ϋά¥‘ΫΗΏΒΡΙΠ¬ ΟήΕ»“Σ«σΘΜΕχ«“Θ§’βϥ¢ΒΡ δ»κΒγ―ΙΫΪΕ‘”ΠΚήΗΏΒΡ δ»κΒγΝςΘ§‘ωΦ”ΝΥœΒΆ≥ΒΡΥπΚΡΘ§ Ι“χΚ–”κΡΗΑε÷°Φδ±Ψ“―ΚήΗ¥‘”ΒΡΝ§Ϋ”œΏ±δΒΟΗϋΡ―…ηΦΤΓΘ

Ω…ΦϊΘ§¥”Βγ‘¥œΒΆ≥Ϋ«Ε»ΩΦ¬«Θ§‘Ύ¬ζΉψΑ≤Ιφ“Σ«σΒΡ«ιΩωœ¬Θ§œΘΆϊVRMΒΡ δ»κΉήœΏΒγ―Ι‘ΫΗΏ‘ΫΚΟΓΘ

ΆΦ8 ΒΞΆ®ΒάQSWΒγ¬ΖΒΡΒδ–ΆΫαΙΙ ΆΦ9 (a) ΡήΝΩΙΊœΒ (b) Cin”κVinΒΡΙΊœΒ«ζœΏ

(3) Vin=2V0ΒΡΆΊΤΥ”≈ Τ”κΗΏΉήœΏ δ»κΒγ―Ι”≈ ΤΒΡΫαΚœΘΚ

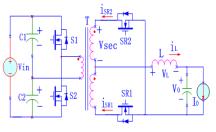

ΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΒγ¬ΖΕ‘”ΠVin=2V0 ±Θ§Βγ¬ΖΆΊΤΥ±Ψ…μΨΏ”–ΚήΚΟΒΡ–‘ΡήΓΘΒΪ¥”’ϊΗωΦΤΥψΜζΒγ‘¥œΒΆ≥Ϋ«Ε»ΩΦ¬«Θ§VinΧΪΒΆΘ§Μα¥σ¥σ‘ωΦ”œΒΆ≥…ηΦΤΒΡΡ―Ε»ΓΘΈΣΝΥΫβΨω’β“ΜΟ§ΕήΘ§ΡήΙΜΆ§ ±άϊ”ΟΝΫΖΫΟφΒΡ”≈ ΤΘ§ΩΦ¬«“ΐ»κΗτάκ±δ―ΙΤςΘ§άϊ”ΟΤδ‘―±»±δΜΜΙΊœΒΘ§Α―ΗΏΉήœΏ δ»κΒγ―Ι±δΜΜΈΣΒΆ δ»κΒγ―ΙΘ§Ά§ ±ΫαΚœΫΜ¥μ≤ΔΝΣQSWΦΦ θΘ§ΒΟΒΫΥυœΘΆϊΒΡΒΆ δ≥ωΒγ―ΙΓΘΜυ±ΨΥΦ¬Ζ”–ΝΫ÷÷ΘΚ

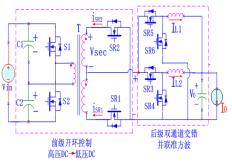

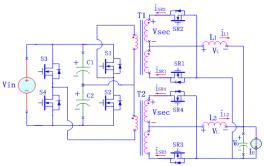

ΔΌ ΝΫΦΕΫαΙΙΘ®»γΆΦ10Θ©ΘΚ(ΗΏ―Ι/ΒΆ―Ι)ΒΡDC/DC«ΑΦΕΘΪΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΚσΦΕΓΘΗΟΖΫΑΗΒΡΚσΦΕΩ…“‘÷±Ϋ”≤…”ΟΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΒγ¬ΖΘ§ΤδΙΊΦϋ‘Ύ”Ύ«ΑΦΕΒΆ―ΙDC δ≥ωΒΡΒΟΒΫΓΘ

ΆΦ10 ΝΫΦΕΫαΙΙ Ψ“βΆΦ

ΔΎ Ητάκ ΫΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥΘ®»γΆΦ11Θ©ΘΚ≤…”ΟΗτάκ ΫΆΊΤΥΘ§ΫαΚœQSWΚΆΫΜ¥μ≤ΔΝΣΦΦ θΘ§ Βœ÷ΗΏΉήœΏ δ»κΒγ―ΙΒΫΒΆ―Ι δ≥ωΒΡ±δΜΜΓΘ

ΆΦ11 Ητάκ ΫΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥ

5 ”Π”ΟQSWΒΡΗτάκ ΫΆΊΤΥ

5.1 ΝΫΦΕΖΫΑΗ

ΝΫΦΕΖΫΑΗ÷–Θ§«ΑΦΕΒΡ(ΗΏ―Ι/ΒΆ―Ι) DC/DC±δΜΜΘ§Ω…≤…”ΟΒΡΆΊΤΥ–Έ ΫΫœΕύΓΘ»γΙϊ≤…”Ο≥ΘΙφΖΫΖ®Θ§±Ί»Μ–η“Σ“ΜΧΉΆξ’ϊΒΡΩΊ÷ΤΒγ¬ΖΓΔ±’ΜΖ…ηΦΤΘ§‘ωΦ”ΝΥ‘ΣΦΰ ΐΚΆ’ϊΜζΒΡΗ¥‘”≥ΧΕ»ΓΘΒΪ»γΙϊΉΔ“βΒΫΘ§Β±±δ―ΙΤςΗ±±Ώ≤…”Ο»Ϊ≤®’ϊΝςΘ®Μρ»Ϊ«≈’ϊΝςΘ©Θ§‘≠±Ώ≤…”ΟΕ‘≥ΤΆΊΤΥ(»γΆΤΆλΓΔ«≈ Ϋ)Θ§ΩΣΙΊΙή¬ζ’ΦΩ’±»ΩΣΜΖΩΊ÷Τ ±Θ§±δ―ΙΤς»ΤΉι…œΩ…“‘ΒΟΒΫΕ‘≥ΤΒΡΖΫ≤®Βγ―ΙΘ§’ϊΝςΚσΡήΙΜΒΟΒΫ±»ΫœάμœκΒΡΒΆ―Ι÷±ΝςΓΘ»γΆΦ12ΈΣΓΑΕ‘≥ΤΑκ«≈»Ϊ≤®’ϊΝς+ΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΓ±ΆΊΤΥΓΘΤδ÷ς“ΣΙΛΉς≤®–Έ Ψ”ΎΆΦ12Θ§‘Ύ’β÷÷ΝΫΦΕΆΊΤΥΫαΙΙ÷–Θ§‘≠±ΏΩΣΙΊS1ΓΔS2≤…”ΟΩΣΜΖΩΊ÷ΤΘ§ΙΧΕ®‘Ύ¬ζ’ΦΩ’±»Θ§Η±±ΏSR1ΓΔSR2Ιή≤…”ΟΉ‘«ΐΕ·ΖΫΖ®Θ§QSW÷–ΒΡSR3-SR6≤…”Ο”κΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΒγ¬ΖœύΆ§ΒΡΩΊ÷ΤΖΫΖ®ΓΘ’β÷÷ΖΫΑΗ¥σ¥σΦρΜ·ΝΥΩΊ÷ΤΒγ¬Ζ…ηΦΤΓΘ

ΆΦ12 ΓΑΕ‘≥ΤΑκ«≈»Ϊ≤®’ϊΝς+ΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΓ±ΆΊΤΥΦΑΤδ÷ς“ΣΙΛΉς≤®–Έ

5.2 Ητάκ ΫΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΆΊΤΥ

(1) Ητάκ Ϋ±δΜΜΤςΆΊΤΥΒΡΦρΒΞΜΊΙΥ

ΆΦ13Ηχ≥ωΝΥΦΗ÷÷≥Θ”ΟΒΡΗτάκ ΫDC/DC±δΜΜΤςΆΊΤΥΘ§(a)”–‘¥σιΈΜ’ΐΦΛΘΜ(b)Ζ¥ΦΛΘΜ(c)Ε‘≥ΤΆΊΤΥΘΚΆΤΆλΓΔΑκ«≈ΓΔ»Ϊ«≈ΓΘΤδ÷–Θ§Ε‘≥ΤΆΊΤΥ÷ΜΗχ≥ωΝΥ‘≠±ΏΆΊΤΥΓΘ

(a) ”–‘¥σιΈΜ’ΐΦΛ (b) Ζ¥ΦΛ

(a) ”–‘¥σιΈΜ’ΐΦΛ (b) Ζ¥ΦΛ

(c) Ακ«≈ ΆΤΆλ »Ϊ«≈

ΆΦ13 ΦΗ÷÷≥Θ”ΟΒΡΗτάκ ΫDC/DC±δΜΜΤςΆΊΤΥ ΆΦ14 ’ΐΦΛ±δΜΜΤςΗΚ‘ΊΥ≤±δΙΛΉς≤®–Έ

Ε‘”Ύ’ΐΦΛ±δΜΜΤςΘ§Ήή–η“ΣΝτ”–“ΜΕ®ΝΩΒΡ’ΦΩ’±»”Ο”Ύ±δ―ΙΤςΧζ–ΨΒΡ¥≈Η¥ΈΜΓΘ‘Ύ’βΕΈΧζ–Ψ¥≈Η¥ΈΜ ±ΦδΡΎΘ§‘≠±Ώ≤ΜœρΗ±±Ώ¥Ϊ δΡήΝΩΓΘ“ρ¥Υ’ΐΦΛ ΫΆΊΤΥ≤ΜΩ…ΡήœσΉΦΖΫ≤®ΆΊΤΥΡ«―υΙΛΉς‘Ύ100ΘΞΒΡ’ΦΩ’±»ΓΘ»γΆΦ14Υυ ΨΘ§ΈΣ’ΐΦΛ±δΜΜΤςΒΡΙΛΉς≤®–ΈΓΘΦ¥ Ι‘ΎΗΚ‘ΊΆΜ…ΐ ±Θ§“ΜΗω÷ήΤΎ÷–»‘»Μ±Ί–κ±ΘΝτ“ΜΕΈ ±Φδ”Ο”ΎΒγΗ–Ζ≈ΡήΘ§’βΨΆ ΙΒΟ’ΐΦΛ ΫΆΊΤΥΒΡœλ”ΠΥΌΕ»“Σ±»QSWΒγ¬Ζ¬ΐΓΘΕχΈΣΝΥ¬ζΉψΩλœλ”ΠΥΌΕ»ΒΡ“Σ«σΘ§±Ί»Μ“Σ¥σ¥σ‘ω¥σ¥≈–‘‘ΣΦΰΒΡΧεΜΐΘ§“‘±Θ÷ΛΗΚ‘ΊΆΜ…ΐΤΎΦδΘ§±δΜΜΤςΩλΥΌΧα…ΐ’ΦΩ’±» ±Θ§ΒγΗ–ΚΆ±δ―ΙΤς≤ΜΜα±ΞΚΆΓΘ

Ζ¥ΦΛ ΫΆΊΤΥ“≤¥φ‘ΎœύΥΤΒΡΈ ΧβΘ§“ρΤδ±δ―ΙΤς ΒΦ …œΈΣώνΚœΒγΗ–Θ§‘ΎΗΚ‘ΊΆΜ…ΐ ±Θ§±Ί–κ Ήœ»Ηχ¥≈Μ·ΒγΗ–¥ΔΡήΘ§»ΜΚσ‘Ό¥”‘≠±ΏœρΗ±±Ώ¥ΪΥΆΡήΝΩΓΘ’β ΙΒΟœλ”Π≥ωœ÷―”≥ΌΓΘ

ΆΤΆλΓΔ«≈ ΫΒγ¬ΖΈΣ±δ―ΙΤςΕ‘≥ΤΙΛΉςΒΡΆΊΤΥΘ§Ω…“‘‘Ύ’ϊΗω÷ήΤΎΕΦ¥”‘≠±ΏœρΗ±±Ώ¥ΪΥΆΡήΝΩΓΘ“ρΕχΘ§Ε‘≥ΤΙΛΉςΒΡΆΊΤΥΨΏ±ΗQSWΒγ¬ΖΡ«―υΩλœλ”ΠΒΡΩ…ΡήΓΘΩΦ¬«ΒΫΆΤΆλΆΊΤΥ¥φ‘Ύ±δ―ΙΤς¬©Η–“ΐΤπΒΡΙΊΕœΒγ―ΙΦβΖεΒ»Έ ΧβΘ§»Ϊ«≈Βγ¬Ζ–η“ΣΥΡΙήΘ§«ΐΕ·Η¥‘”Β»Έ ΧβΘ§‘ΎœύΕ‘ΫœΗΏ δ»κΒγ―Ι ±(»γ48VΉήœΏΒγ―Ι)Θ§≤…”ΟΕ‘≥ΤΑκ«≈Βγ¬ΖΉςΈΣ÷ςΒγ¬ΖΆΊΤΥ±»ΫœΚœ ΓΘ

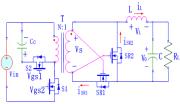

(2) QSWΕ‘≥ΤΑκ«≈ΆΊΤΥ

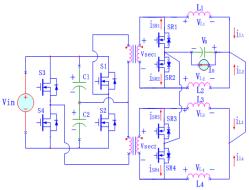

Ε‘”ΎΑκ«≈ΆΊΤΥΘ§Η±±ΏΒΡ’ϊΝςΒγ¬ΖΩ…≤…”ΟΆΦ15ΒΡ÷––Ρ≥ιΆΖ»Ϊ≤®’ϊΝςΫαΙΙ(a)ΚΆ±ΕΝς’ϊΝςΫαΙΙ(b)ΓΘ

ΆΦ15 (a) Ε‘≥ΤΑκ«≈»Ϊ≤®’ϊΝςΒγ¬Ζ (b) QSWΙΛΉς≤®–Έ

»γΆΦ15Υυ ΨΘ§»ΟΕ‘≥ΤΑκ«≈»Ϊ≤®’ϊΝςΒγ¬ΖΑ¥’’QSWΖΫ ΫΙΛΉςΘ§‘ΎΥυ”–ΗΚ‘ΊΖΕΈßΡΎΒγΗ–ΒγΝςΕΦ¥”’ΐΒΫΗΚ±δΜ·Θ§‘ρΩ… Βœ÷‘≠±ΏΩΣΙΊΙή‘ΎΩΣΆ®÷°«ΑΘ§ΒγΗ–ΒγΝςΖ¥”≥ΒΫ‘≠±ΏΘ§ΝςΙΐΦ¥ΫΪΩΣΆ®ΒΡΩΣΙΊΙήΒΡΧεΕΰΦΪΙήΘ§ Βœ÷ZVSΓΘΕχ«“‘ΎΗΚ‘ΊΆΜ…ΐ ±Θ§ δ≥ω¬Υ≤®ΒγΗ–ΒΡΒ»–ß’ΦΩ’±»Ω…¥οΒΫ100%Θ§’ϊΗω÷ήΤΎΕΦΜα”–’ΐ―ΙΦ”‘Ύ δ≥ω¬Υ≤®ΒγΗ–…œΘ§ά¥Χα…ΐΒγΝςΘΜΗΚ‘ΊΆΜΫΒ ±Θ§¬Υ≤®ΒγΗ–ΒΡΒ»–ß’ΦΩ’±»Ω…“‘ΈΣ0%Θ§’ϊΗω÷ήΤΎΕΦΜα”–ΗΚ―ΙΦ”‘ΎΒγΗ–…œΘ§ά¥ΫΒΒΆΒγΝςΓΘΨΏ”–”κΒΞΆ®ΒάQSWΒγ¬ΖœύΥΤΒΡΕ·Χ§œλ”ΠΧΊ–‘ΓΘ”Π”ΟΫΜ¥μ≤ΔΝΣΦΦ θΘ§Α―ΝΫΗωΕ‘≥ΤΑκ«≈»Ϊ≤®’ϊΝςΒγ¬Ζ≤ΔΝΣΤπά¥(»γΆΦ16)Θ§»ΓΈ»Χ§’ΦΩ’±»ΈΣ0.5Θ§Ω… Βœ÷Άξ»ΪΒΡ δ≥ωΒγΝςΈΤ≤®ΜΞœϊΉς”ΟΘ§¥σ¥σΦθ–Γ δ≥ω¬Υ≤®ΤςΘ§‘ΎΗΚ‘ΊΆΜ…ΐΚΆΗΚ‘ΊΆΜΫΒ ±Θ§ΨΏ”–Ε‘≥ΤΒΡΩλΕ·Χ§œλ”ΠΓΘ

ΆΦ16 ΫΜ¥μ≤ΔΝΣΕ‘≥ΤΑκ«≈»Ϊ≤®’ϊΝςΒγ¬Ζ ΆΦ17 Ε‘≥ΤΑκ«≈±ΕΝς’ϊΝςΆΊΤΥ

»γΆΦ17ΈΣΕ‘≥ΤΑκ«≈±ΕΝς’ϊΝςΆΊΤΥΘ§ΝΫΗω δ≥ω¬Υ≤®ΒγΗ–ΒΡΒγΝςœύΈΜœύ≤ν180oΘ§”κΥΪΆ®ΒάΫΜ¥μ≤ΔΝΣΆΊΤΥ¥φ‘ΎœύΥΤΒΡΒγΗ–ΒγΝςΈΤ≤®ΜΞœϊΉς”ΟΘ§Ε‘”ΠD=0.5 ±Θ§Ω…“‘ Βœ÷Άξ»ΪΒΡΒγΝςΈΤ≤®ΜΞœϊΉς”ΟΘ® δ≥ωΒγΝςΈΤ≤®ΈΣΝψΘ©ΓΘ‘Ύ”Π”Ο”ΎΗΚ‘ΊΕ‘Ε·Χ§œλ”Π“Σ«σ≤ΜΗΏΒΡ≥ΓΚœ ±Θ§Ω…“‘Α―Έ»Χ§’ΦΩ’±»―ΓΕ®ΈΣ0.5Θ§¥”Εχ¥σ¥σΦθ–Γ δ≥ω¬Υ≤®ΤςΒΡΧεΜΐΓΘΒΪΕ‘”Ύ ΐΨί¥ΠάμΤς’βάύΕ‘Ε·Χ§œλ”Π”–ΫœΗΏ“Σ«σΒΡΗΚ‘Ί ±Θ§≤ΜΡήΑ―0.5’β“Μ¬ζ’ΦΩ’±»ΉςΈΣΈ»Χ§’ΦΩ’±»ΓΘΒΪΒ±DΤΪάκ0.5 ±Θ§ΤδΈΤ≤®ΜΞœϊΉς”Ο‘ρΜα¥σ¥σœς»θΘ§œό÷ΤΝΥ δ≥ω¬Υ≤®Τς≤Έ ΐΒΡ»Γ–ΓΘ§ΫΒΒΆΝΥΙΠ¬ ΦΕΒΡΡήΝΩ¥Ϊ δΥΌΕ»ΓΘ‘Ύ’β÷÷«ιΩωœ¬άϊ”ΟΫΜ¥μ≤ΔΝΣΦΦ θΘ§Α―ΝΫΗωΕ‘≥ΤΑκ«≈±ΕΝς’ϊΝςΆΊΤΥΫχ––ΫΜ¥μ≤ΔΝΣΘ§»γΆΦ18Υυ ΨΘ§‘ρΩ… Βœ÷”κΥΡΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΒγ¬ΖœύΥΤΒΡΈΤ≤®ΜΞœϊΉς”ΟΘ®“ρDmaxΘΦ0.5Θ§«Α’Ώ÷Μ”–Κσ’ΏΜΞœϊ«ζœΏΒΡΑκ÷ßΘ©Θ§¥Υ ±Θ§»τΑ―Έ»Χ§’ΦΩ’±»Ε®‘Ύ0.25Θ§‘ρΩ… Βœ÷Έ»Χ§ ±Άξ»ΪΒΡΈΤ≤®ΜΞœϊΉς”ΟΘ§ δ≥ω¬Υ≤®ΒγΗ–“≤Ω…“‘»ΓΒΟΚή–ΓΘ§¥”Εχ‘ΎΗΚ‘ΊΆΜ…ΐ(DΘΚ0.25Γζ0.5)ΚΆΆΜΫΒ(DΘΚ0.25Γζ0) ±Θ§ΨΏ”–Ε‘≥ΤΒΡΩλΕ·Χ§œλ”ΠΓΘ

ΆΦ18 ΫΜ¥μ≤ΔΝΣΕ‘≥ΤΑκ«≈±ΕΝς’ϊΝςΆΊΤΥΦΑΤδ‘≠άμ≤®–Έ

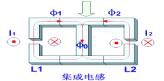

ΧΊ±π÷ΒΒΟ÷Η≥ωΒΡ «Θ§’β–©ΫΜ¥μ≤ΔΝΣΫαΙΙΒΡΆΊΤΥΧΊ±π Κœ”Ύ”Π”Ο¥≈Φ·≥…ΦΦ θΓΘ“ΜΑψΩ…≤…”ΟΝΫ÷÷Φ·≥…ΥΦ¬ΖΘΚΕύΆ®ΒάΒγΗ–ΒΡΦ·≥…Θ§“‘ΦΑΒγΗ–ΚΆ±δ―ΙΤςΒΡΦ·≥…ΓΘ

ΔΌ ‘ΎΫΜ¥μ≤ΔΝΣΫαΙΙ÷–Θ§Υδ»Μ”…ΕύΆ®ΒάΒγΗ–ΒγΝςΫΜ¥μΚœ≥…ΚσΒΡΉήΒγΝςΤδΈΤ≤®Ϋœ–ΓΘ§ΒΪΝςΙΐΟΩΗωΖ÷ΝΔΒγΗ–…œΒΡΒγΝςΈΤ≤®»¥Ϋœ¥σΘ§Ε‘”ΠΟΩ÷ΜΒγΗ–ΒΡ¥≈Ά®¬ωΕ·ΝΩΫœ¥σΘ§“ΐΤπΫœ¥σΒΡΧζ–ΨΥπΚΡΘ§ΫΒΒΆΝΥ’ϊΜζ–߬ ΘΜ»τΑ―Εύ÷ΜΖ÷ΝΔΒγΗ–Φ·≥…‘Ύ“Μ÷ΜΧζ–Ψ…œΘ®»γΆΦ19ΈΣΝΫΆ®ΒάΒγΗ–ΒΡΦ·≥… Ψ“βΆΦΘ©Θ§¥≈Ά®‘Ύ÷––Ρ÷υ…œΫΜΒΰΘ§Ω…“‘ Βœ÷¥≈Ά®¬ωΕ·ΝΩΒΡΜΞœϊΉς”ΟΘ§¥”Εχ¥σ¥σΦθ–Γ÷––Ρ÷υΒΡΧζ–ΨΥπΚΡΚΆΧζ–ΨΧεΜΐΓΘ

ΔΎ ‘Ύ±ΕΝς’ϊΝςΆΊΤΥ÷–Θ§Ω…Α―±δ―ΙΤςΚΆΝΫΗωΖ÷ΝΔΒγΗ–Φ·≥…‘Ύ“Μ÷ΜΧζ–Ψ…œΘ§»γΆΦ20Υυ ΨΘ§Ά§ ± Βœ÷ΝΥΧζ–ΨΚΆ»ΤΉιΒΡΦ·≥…Θ§¥”Εχ¥σ¥σΦθ–ΓΝΥ¥≈–‘‘ΣΦΰΥυ’ΦΒΡΉήΧεΜΐΘ§ΦρΜ·ΝΥΒγ¬Ζ≤ΦΨ÷ΓΔΖβΉΑ…ηΦΤΘ§”κΖ÷ΝΔ¥≈–‘‘ΣΦΰœύ±»Θ§ΨΏ”–œ‘÷χΒΡ”≈‘Ϋ–‘ΓΘ

ΆΦ19 (a)ΝΫΒγΗ–Χζ–ΨΦ·≥… Ψ“β (b)¥≈Ά®¬ωΕ·ΜΞœϊΉς”Ο Ψ“βΆΦ ΆΦ20 »ΐΗωΖ÷ΝΔ¥≈–‘‘ΣΦΰΒΡΦ·≥…

6 Ϋα ”ο

±ΨΤΣ’κΕ‘ΈΔ¥ΠάμΤς”Π”Ο≥ΓΚœΘ§Ε‘ΤδΙ©ΒγΒγ‘¥VRMΫχ––ΝΥΆΊΤΥΖ÷ΈωΘ§÷Η≥ωœ÷”–ΆΊΤΥΒΡ»±œίΘ§¥”Εχ“ΐ≥ωΉΦΖΫ≤®’ϊΝςΖΫ ΫΘ§≤ΔΕ‘ΤδΫχ––ΝΥ‘≠άμΖ÷ΈωΘ§≤ΔΫαΚœΫΜ¥μ≤ΔΝΣΦΦ θΘ§Ε‘ΕύΆ®ΒάΫΜ¥μ≤ΔΝΣQSWΒγ¬ΖΫχ––ΝΥΖ÷ΈωΘ§‘Ύ¥ΥΜυ¥Γ…œΘ§Ηχ≥ω ΚœΗΏΉήœΏ“Σ«σΒΡΗτάκ ΫΫΜ¥μ≤ΔΝΣQSWΖΫΑΗΘ§Ε‘ΗςΒγ¬ΖΧΊΒψΫχ––ΝΥ≤ϊ ωΓΘ±ΨΈΡΖ÷Έω”–÷ζ”ΎQSW‘ΎVRM÷–ΒΡΚœάμ―Γ”ΟΚΆΒγ¬Ζ÷ΤΉςΓΘ

≤ΈΩΦΈΡœΉΘΚ

[1] Fred C.Lee and Xunwei zhou, Investigaion of Power Management Issues for Future Generation Miroprocessors, CPES

[2] Michael T.Zhang, Milan M.Jovanovic and Fred C.Lee,ΓΑDesign Considerations for Low-Voltage On-board DC-DC Modules for Next Generations of Data Processing Circuits,Γ±IEEE Transactions on Power Electronics,Vol.11,No.2 March 1996

[3] Xunwei Zhou, Xingzhu Zhang,Jiangang Liu,Pit-leong,Jiabin Chen,Ho-PuWu,Luca Amoroso,Fred C.Lee,and Dan Y.Chen,ΓΑInvestigation of Candidate VRM Topologies for future Microprocessors,Γ±,IEEE APECΓ·98 conf.

[4] P.Wong,X.Zhou,J.Chen,H.Wu,L,Amoroso,J.Liu,F.C.Lee,X.Zhang and D.Y.Chen,ΓΑVRM Transience Study and Output Filter Design for Future Processors,Γ±VPEC Seminar1997

[5] Yuri Panov and Milan M.Jovanovic, Design and Performance Evaluation of Low-Voltage/High-Current Dc/Dc On-Board Modules ,APECΓ·99,pp545~552

[6] Pit-Leong,Xunwei Zhou,Bo Yang and Fred C.LeeΘ§ΓΑFast VRM with High Input VoltageΓ±VPEC Seminar. 1998

[7] W.Chen,F.C.Lee,X.Zhou and P.Xu,ΓΑIntegrated Planar Inductor Scheme for Multi-module interleaved Quasi-Squre-Wave DC/DC ConverterΓ±Θ§IEEE PESCΓ·99

[8] Art Brockschmidt,ΓΑOptimizing Distribution Bus VoltagesΓ±,IEEE APECΓ·98

[9] W.Chen, G.Hua, D.Sable,F.C.Lee, Design of high-efficiency, low-profile, low-voltage converter with integrated magnetics, IEEE APEC,pp911~917.

[10] Pit-Leong, Xunwei Bo Yang, Peng Xu and Fred C.LeeΘ§ΓΑQuasi-Square-Wave Rectification for Front-End DC/DC Converters.Γ±IEEE PESCΓ·2000

[11] ΕΓΒάΚξΘ§ΓΕΒγΝΠΒγΉ”ΦΦ θΓΖΘ§ΚΫΩ’ΙΛ“Β≥ωΑφ…γΘ§±±Ψ©Θ§1995

[12] »ν–¬≤®Θ§―œ―ωΙβΘ§ΓΕ÷±ΝςΩΣΙΊΒγ‘¥ΒΡ»μΩΣΙΊΦΦ θΓΖΘ§ΩΤ―ß≥ωΑφ…γΘ§2000

[13] ≤Χ–ϊ»ΐΓΔΙ®…ήΈΡΘ§ΓΕΗΏΤΒΙΠ¬ ΒγΉ”―ßΓΣ÷±Νς-÷±Νς±δΜΜ≤ΩΖ÷ΓΖΘ§ΩΤ―ß≥ωΑφ…γΘ§1993